# CP6007-SA, CP6007-RA

User Guide, Rev. 1.2 Doc. ID: 1070-2698

This page has been intentionally left blank

## ► CP6007-SA, CP6007-RA - USER GUIDE

#### Disclaimer

Kontron would like to point out that the information contained in this user guide may be subject to alteration, particularly as a result of the constant upgrading of Kontron products. This document does not entail any guarantee on the part of Kontron with respect to technical processes described in the user guide or any product characteristics set out in the user guide. Kontron assumes no responsibility or liability for the use of the described product(s), conveys no license or title under any patent, copyright or mask work rights to these products and makes no representations or warranties that these products are free from patent, copyright or mask work right infringement unless otherwise specified. Applications that are described in this user guide are for illustration purposes only. Kontron makes no representation or warranty that such application will be suitable for the specified use without further testing or modification. Kontron expressly informs the user that this user guide only contains a general description of processes and instructions which may not be applicable in every individual case. In cases of doubt, please contact Kontron.

This user guide is protected by copyright. All rights are reserved by Kontron. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), without the express written permission of Kontron. Kontron points out that the information contained in this user guide is constantly being updated in line with the technical alterations and improvements made by Kontron to the products and thus this user guide only reflects the technical status of the products by Kontron at the time of publishing.

Brand and product names are trademarks or registered trademarks of their respective owners.

©2025 by Kontron Europe GmbH

Kontron Europe GmbH

Gutenbergstraße 2 85737 Ismaning Germany www.kontron.com

#### Intended Use

THIS DEVICE AND ASSOCIATED SOFTWARE ARE NOT DESIGNED, MANUFACTURED OR INTENDED FOR USE OR RESALE FOR THE OPERATION OF NUCLEAR FACILITIES, THE NAVIGATION, CONTROL OR COMMUNICATION SYSTEMS FOR AIRCRAFT OR OTHER TRANSPORTATION, AIR TRAFFIC CONTROL, LIFE SUPPORT OR LIFE SUSTAINING APPLICATIONS, WEAPONS SYSTEMS, OR ANY OTHER APPLICATION IN A HAZARDOUS ENVIRONMENT, OR REQUIRING FAIL-SAFE PERFORMANCE, OR IN WHICH THE FAILURE OF PRODUCTS COULD LEAD DIRECTLY TO DEATH, PERSONAL INJURY, OR SEVERE PHYSICAL OR ENVIRONMENTAL DAMAGE (COLLECTIVELY, "HIGH RISK APPLICATIONS").

You understand and agree that your use of Kontron devices as a component in High Risk Applications is entirely at your risk. To minimize the risks associated with your products and applications, you should provide adequate design and operating safeguards. You are solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning your products. You are responsible to ensure that your systems (and any Kontron hardware or software components incorporated in your systems) meet all applicable requirements. Unless otherwise stated in the product documentation, the Kontron device is not provided with error-tolerance capabilities and cannot therefore be deemed as being engineered, manufactured or setup to be compliant for implementation or for resale as device in High Risk Applications. All application and safety related information in this document (including application descriptions, suggested safety measures, suggested Kontron products, and other materials) is provided for reference only.

Handling and operation of the product is permitted only for trained personnel within a work place that is access controlled. Please follow the "General Safety Instructions for IT Equipment" supplied with the system.

## **Revision History**

| Revision | Brief Description of Changes                | Date of Issue | Author/<br>Editor |

|----------|---------------------------------------------|---------------|-------------------|

| 1.0      | Initial Version                             | 2022-May-23   | MK                |

| 1.1      | Corrections in chapter 2.7.7. "M.2 Socket". | 2025-Feb-20   | MK                |

| 1.2      | M.2 Socket SSD, optionally double sided     | 2025-Dec-04   | CW                |

## **Terms and Conditions**

Kontron warrants products in accordance with defined regional warranty periods. For more information about warranty compliance and conformity, and the warranty period in your region, visit <a href="http://www.kontron.com/terms-and-conditions">http://www.kontron.com/terms-and-conditions</a>.

Kontron sells products worldwide and declares regional General Terms & Conditions of Sale, and Purchase Order Terms & Conditions. Visit http://www.kontron.com/terms-and-conditions.

For contact information, refer to the corporate offices contact information on the last page of this user guide or visit our website <u>CONTACT US</u>.

## **Customer Support**

Find Kontron contacts by visiting: <a href="http://www.kontron.com/support">http://www.kontron.com/support</a>.

## **Customer Service**

As a trusted technology innovator and global solutions provider, Kontron extends its embedded market strengths into a services portfolio allowing companies to break the barriers of traditional product lifecycles. Proven product expertise coupled with collaborative and highly-experienced support enables Kontron to provide exceptional peace of mind to build and maintain successful products.

For more details on Kontron's service offerings such as: enhanced repair services, extended warranty, Kontron training academy, and more visit <a href="http://www.kontron.com/support-and-services/services">http://www.kontron.com/support-and-services/services</a>.

#### **Customer Comments**

If you have any difficulties using this user guide, discover an error, or just want to provide some feedback, contact <u>Kontron support</u>. Detail any errors you find. We will correct the errors or problems as soon as possible and post the revised user guide on our website.

<u>www.kontron.com</u> // 5

## **Symbols**

The following symbols may be used in this user guide

**ADANGER**

DANGER indicates a hazardous situation which, if not avoided, will result in death or serious injury.

**AWARNING**

WARNING indicates a hazardous situation which, if not avoided, could result in death or serious injury.

NOTICE

NOTICE indicates a property damage message.

**A**CAUTION

CAUTION indicates a hazardous situation which, if not avoided, may result in minor or moderate injury.

Electric Shock!

This symbol and title warn of hazards due to electrical shocks (> 60 V) when touching products or parts of products. Failure to observe the precautions indicated and/or prescribed by the law may endanger your life/health and/or result in damage to your material.

**ESD Sensitive Device!**

This symbol and title inform that the electronic boards and their components are sensitive to static electricity. Care must therefore be taken during all handling operations and inspections of this product in order to ensure product integrity at all times.

**HOT Surface!**

Do NOT touch! Allow to cool before servicing.

Laseri

This symbol inform of the risk of exposure to laser beam and light emitting devices (LEDs) from an electrical device. Eye protection per manufacturer notice shall review before servicing.

This symbol indicates general information about the product and the user guide.

This symbol also indicates detail information about the specific product configuration.

This symbol precedes helpful hints and tips for daily use.

## For Your Safety

Your new Kontron product was developed and tested carefully to provide all features necessary to ensure its compliance with electrical safety requirements. It was also designed for a long fault-free life. However, the life expectancy of your product can be drastically reduced by improper treatment during unpacking and installation. Therefore, in the interest of your own safety and of the correct operation of your new Kontron product, you are requested to conform with the following guidelines.

### **High Voltage Safety Instructions**

As a precaution and in case of danger, the power connector must be easily accessible. The power connector is the product's main disconnect device.

#### Warning

All operations on this product must be carried out by sufficiently skilled personnel only.

#### Electric Shock!

Before installing a non hot-swappable Kontron product into a system always ensure that your mains power is switched off. This also applies to the installation of piggybacks. Serious electrical shock hazards can exist during all installation, repair, and maintenance operations on this product. Therefore, always unplug the power cable and any other cables which provide external voltages before performing any work on this product.

Earth ground connection to vehicle's chassis or a central grounding point shall remain connected. The earth ground cable shall be the last cable to be disconnected or the first cable to be connected when performing installation or removal procedures on this product.

## Special Handling and Unpacking Instruction

#### ESD Sensitive Device!

Electronic boards and their components are sensitive to static electricity. Therefore, care must be taken during all handling operations and inspections of this product, in order to ensure product integrity at all times.

Do not handle this product out of its protective enclosure while it is not used for operational purposes unless it is otherwise protected.

Whenever possible, unpack or pack this product only at EOS/ESD safe work stations. Where a safe work station is not guaranteed, it is important for the user to be electrically discharged before touching the product with his/her hands or tools. This is most easily done by touching a metal part of your system housing.

It is particularly important to observe standard anti-static precautions when changing piggybacks, ROM devices, jumper settings etc. If the product contains batteries for RTC or memory backup, ensure that the product is not placed on conductive surfaces, including anti-static plastics or sponges. They can cause short circuits and damage the batteries or conductive circuits on the product.

### **Lithium Battery Precautions**

If your product is equipped with a lithium battery, take the following precautions when replacing the battery.

#### **A**CAUTION

#### Danger of explosion if the battery is replaced incorrectly.

- Replace only with same or equivalent battery type recommended by the manufacturer.

- Dispose of used batteries according to the manufacturer's instructions.

## General Instructions on Usage

In order to maintain Kontron's product warranty, this product must not be altered or modified in any way. Changes or modifications to the product, that are not explicitly approved by Kontron and described in this user guide or received from Kontron Support as a special handling instruction, will void your warranty.

This product should only be installed in or connected to systems that fulfill all necessary technical and specific environmental requirements. This also applies to the operational temperature range of the specific board version that must not be exceeded. If batteries are present, their temperature restrictions must be taken into account.

In performing all necessary installation and application operations, only follow the instructions supplied by the present user guide.

Keep all the original packaging material for future storage or warranty shipments. If it is necessary to store or ship the product then re-pack it in the same manner as it was delivered.

Special care is necessary when handling or unpacking the product. See Special Handling and Unpacking Instruction.

## Quality and Environmental Management

Kontron aims to deliver reliable high-end products designed and built for quality, and aims to complying with environmental laws, regulations, and other environmentally oriented requirements. For more information regarding Kontron's quality and environmental responsibilities, visit <a href="http://www.kontron.com/about-kontron/corporate-responsibility/quality-management">http://www.kontron.com/about-kontron/corporate-responsibility/quality-management</a>.

#### Disposal and Recycling

Kontron's products are manufactured to satisfy environmental protection requirements where possible. Many of the components used are capable of being recycled. Final disposal of this product after its service life must be accomplished in accordance with applicable country, state, or local laws or regulations.

#### **WEEE Compliance**

The Waste Electrical and Electronic Equipment (WEEE) Directive aims to:

- Reduce waste arising from electrical and electronic equipment (EEE)

- Make producers of EEE responsible for the environmental impact of their products, especially when the product become waste

- Encourage separate collection and subsequent treatment, reuse, recovery, recycling and sound environmental disposal of EEE

- Improve the environmental performance of all those involved during the lifecycle of EEE

Environmental protection is a high priority with Kontron.

Kontron follows the WEEE directive

You are encouraged to return our products for proper disposal.

## **Table of Contents**

| Symbols                                    | Е  |

|--------------------------------------------|----|

| For Your Safety                            | 7  |

| High Voltage Safety Instructions           | 7  |

| Special Handling and Unpacking Instruction | 7  |

| Lithium Battery Precautions                | 8  |

| General Instructions on Usage              | 8  |

| Quality and Environmental Management       | 8  |

| Disposal and Recycling                     | 8  |

| WEEE Compliance                            | 8  |

| Table of Contents                          | g  |

| List of Tables                             | 11 |

| List of Figures                            | 13 |

| 1/ Introduction                            | 14 |

| 1.1. Board Overview                        | 14 |

| 1.2. System Expansion Capabilities         | 15 |

| 1.2.1. PMC Module                          | 15 |

| 1.2.2. XMC Module                          | 15 |

| 1.2.3. Rear I/O Module                     | 15 |

| 1.2.4. M.2 Storage                         | 15 |

| 1.3. Board Diagrams                        | 16 |

| 1.3.1. Functional Block Diagram            | 16 |

| 1.3.2. Front Panel                         | 17 |

| 1.3.3. Board Layout                        | 18 |

| 1.4. Technical Specification               | 20 |

| 1.5. Compliance                            |    |

| 1.6. Related Publications                  | 26 |

| 2/ Functional Description                  | 27 |

| 2.1. Processor                             | 27 |

| 2.1.1. Graphics Controller                 | 28 |

| 2.2. Memory                                | 28 |

| 2.3. Watchdog Timer                        | 28 |

| 2.4. Battery                               | 28 |

| 2.5. Flash Memory                          | 29 |

| 2.5.1. SPI Boot Flash for uEFI BIOS        | 29 |

| 2.5.2. M.2 Flash Module                    | 29 |

| 2.6. Security Options                      | 29 |

| 2.6.1. Trusted Platform Module 2.0         | 29 |

| 2.7. Board Interfaces                      | 30 |

| 2.7.1. Front Panel LEDs                    | 30 |

| 2.7.2. USB Interfaces                      | 33 |

| 2.7.3. DisplayPort Interface               | 33 |

| 2.7.4. Serial Ports                        |    |

| 2.7.5. Gigabit Ethernet                    | 35 |

| 2.7.6. SATA Interfaces                     | 3£ |

| 2.7.7. M.2 Socket                          | 36 |

| 2.7.8. PMC Interface                       | 37 |

| 2.7.9. XMC Interface                       | 37 |

|                                            |    |

| 2.7.10. CompactPCI Interface                          | 38 |

|-------------------------------------------------------|----|

| 2.7.11. CompactPCI Connectors                         | 40 |

| 3/ Configuration                                      | 50 |

| 3.1. DIP Switch Configuration                         | 50 |

| 3.1.1. DIP Switch SW3                                 | 50 |

| 3.1.2. DIP Switch SW4                                 | 51 |

| 3.2. System Write Protection                          | 51 |

| 3.3. CP6007-Specific Registers                        | 51 |

| 3.3.1. Write Protection Register (WPROT)              | 52 |

| 3.3.2. Reset Status Register (RSTAT)                  | 53 |

| 3.3.3. Board ID High Byte Register (BIDH)             | 54 |

| 3.3.4. Geographic Addressing Register (GEOAD)         | 54 |

| 3.3.5. Watchdog Timer Control Register (WTIM)         | 55 |

| 3.3.6. Board ID Low Byte Register (BIDL)              | 56 |

| 3.3.7. LED Configuration Register (LCFG)              | 56 |

| 3.3.8. LED Control Register (LCTRL)                   | 57 |

| 3.3.9. General Purpose Output Register (GPOUT)        | 57 |

| 3.3.10. General Purpose Input Register (GPIN)         | 58 |

| 4/ Power Considerations                               | 59 |

| 4.1. System Power                                     | 59 |

| 4.1.1. CP6007 Voltage Ranges                          | 59 |

| 4.1.2. Power Supply Units                             | 59 |

| 4.2. Power Consumption                                | 61 |

| 4.2.1. Power Consumption of the CP6007-SA Accessories | 62 |

| 4.2.2. Power Consumption per Gigabit Ethernet Port    | 63 |

| 4.2.3. Power Consumption of PMC Modules               |    |

| 4.2.4. Power Consumption of XMC Modules               | 63 |

| 5/ Thermal Considerations                             | 64 |

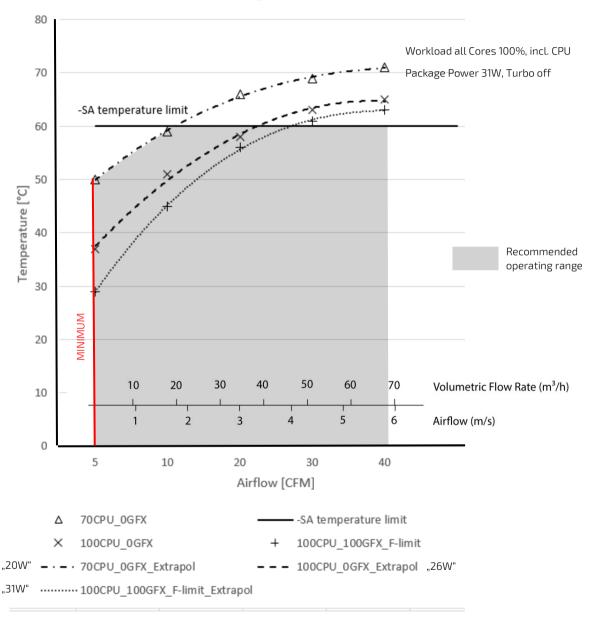

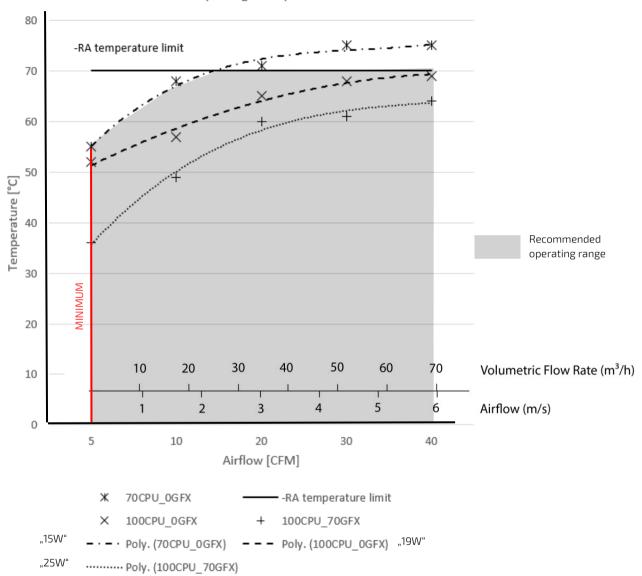

| 5.1. How to read the Temperature Diagrams             | 64 |

| 5.2. Volumetric flow rate                             |    |

| 5.3. Airflow                                          | 64 |

| 5.3.1. Peripherals                                    | 67 |

| 6/ Installation                                       | 68 |

| 6.1. Safety                                           |    |

| 6.2. General Instructions on Usage                    |    |

| 6.3. Board Installation                               |    |

| 6.3.1. Hot Swap Insertion                             |    |

| 6.3.2. Hot Swap Removal                               |    |

| 6.4. Installation of Peripheral Devices               |    |

| 6.4.1. SATA M.2 Module Installation                   |    |

| 6.4.2. Installation of External SATA Devices          |    |

| 6.4.3. PMC Module Installation                        | 73 |

| 6.4.4. XMC Module Installation                        |    |

| 6.4.5. Rear Transition Module Installation            |    |

| 6.5. Battery Replacement                              |    |

| 7/ uEFI BIOS                                          |    |

| 7.1. Starting the uEFI BIOS                           |    |

| 7.2. Setup Menus                                      |    |

| 7.2.1. Main Setup Menu                                | 75 |

| 7.2.2. Advanced Setup Menu                                         |    |

|--------------------------------------------------------------------|----|

| 7.2.3. Security Setup Menu                                         | 77 |

| 7.2.4. Boot Setup Menu                                             | 78 |

| 7.2.5. Exit Setup Menu                                             | 79 |

| 7.3. The uEFI Shell                                                | 80 |

| 7.3.1. Introduction, Basic Operation                               | 80 |

| 7.3.2. Kontron-Specific uEFI Shell Commands                        | 81 |

| 7.4. uEFI Shell Scripting                                          | 82 |

| 7.4.1. Startup Scripting                                           | 82 |

| 7.4.2. Create a Startup Script                                     | 82 |

| 7.4.3. Examples of Startup Scripts                                 | 82 |

| 7.5. Firmware Update                                               | 84 |

| 7.5.1. Updating the uEFI BIOS                                      | 84 |

| 7.5.2. Updating the IPMI Firmware                                  | 86 |

| 8/ IPMI Firmware                                                   | 87 |

| 8.1. Overview                                                      | 87 |

| 8.2. IPMI Firmware and KCS Interface Configuration                 | 87 |

| 8.3. Supported IPMI and PICMG Commands                             | 88 |

| 8.3.1. Standard IPMI Commands                                      |    |

| 8.3.2. PICMG Commands                                              | 91 |

| 8.4. Firmware Identification                                       |    |

| 8.4.1. Get Device ID Command                                       |    |

| 8.4.2. Device Locator Record                                       |    |

| 8.5. Board Control Extensions                                      |    |

| 8.5.1. SPI Boot Flash Selection—uEFI BIOS Failover Control (OPEN)  |    |

| 8.6. Sensors Implemented on the Board                              |    |

| 8.6.1. Sensor List                                                 |    |

| 8.7. Sensor Thresholds                                             |    |

| 8.8. OEM Event/Reading Types                                       |    |

| 8.9. IPMI Firmware Code                                            |    |

| 8.9.1. Firmware Upgrade                                            |    |

| 8.9.2. IPMI Firmware and FRU Data Write Protection                 |    |

| 8.10. LAN Functions                                                |    |

| 9/ Technical Support                                               |    |

| 9.1. Warranty                                                      |    |

| 9.2. Returning Defective Merchandise                               |    |

| Appendix A: List of Acronyms                                       |    |

| About Kontron                                                      |    |

|                                                                    |    |

| List of Tables                                                     |    |

| Table 1: CP6007 Main Specifications                                |    |

| Table 2: Environmental Conditions and Compliance                   |    |

| Table 3: Related Publications                                      |    |

| Table 4: Features of the Processors Supported on the CP6007-SA/-RA |    |

| Table 5: Watchdog and Temperature Status LEDs' Functions           |    |

| Table 7: General Purpose LEDs' Functions on the CP6007             |    |

| Table 8: POST Code Sequence                                        |    |

| Table 9: POST Code Example                                         |    |

|                                                                    |    |

| Table 10: Serial Port Port Connect or J8 Pinout                                                        | 34   |

|--------------------------------------------------------------------------------------------------------|------|

| Table 11: Gigabit Ethernet Controller Port Mapping                                                     | 35   |

| Table 12: PMC PCI Frequency Configuration                                                              | 37   |

| Table 13: CompactPCI PCI / PCI-X Configuration                                                         |      |

| Table 14: CompactPCI Bus Connector J1 System Slot Pinout                                               | 41   |

| Table 15: CompactPCI Bus Connector J1 Peripheral Slot Pinout                                           |      |

| Table 16: 64-bit CompactPCI Bus Connector J2 System Slot Pinout                                        |      |

| Table 17: 64-bit CompactPCI Bus Connector J2 Peripheral Slot Pinout                                    |      |

| Table 18: 64-bit CompactPCI Rear I/O Connector J3 Pinout for CP6007-SA                                 |      |

| Table 19: CompactPCI Rear I/O Connector J3 Signals for CP6007-SA                                       |      |

| Table 20: 64-bit CompactPCI Rear I/O Connector J3 Pinout for CP6007-RA                                 |      |

| Table 21: CompactPCI Rear I/O Connector J3 Signals for CP6007-RA                                       |      |

| Table 22: 64-bit CompactPCI Rear I/O Connector J4 Pinout                                               |      |

| Table 23: CompactPCI Rear I/O Connector J5 Pinout                                                      |      |

| Table 24: CompactPCI Rear I/O Connector J5 Signals                                                     |      |

| Table 25: DIP Switch SW3 Functionality                                                                 |      |

| Table 26: DIP Switch SW4 Functionality                                                                 |      |

| Table 27: CP6007-Specific Registers                                                                    |      |

| Table 28: Write Protection Register (WPROT)                                                            |      |

| Table 29: Reset Status Register (RSTAT)                                                                |      |

| Table 30: Board ID High Byte Register (BIDH)                                                           |      |

| Table 31: Geographic Addressing Register (GEOAD)                                                       |      |

| Table 32: Watchdog Timer Control Register (WTIM)                                                       |      |

| Table 33: Board ID Low Byte Register (BIDL)                                                            |      |

| Table 34: LED Configuration Register (LCFG)                                                            |      |

| Table 35: LED Control Register (LCTRL)                                                                 |      |

| Table 36: General Purpose Output Register (GPOUT)                                                      |      |

| Table 37: General Purpose Input Register (GPIN)                                                        |      |

| Table 38: Operational Input Voltage Range                                                              |      |

| Table 39: Workload: uEFI Shell                                                                         |      |

| Table 40: Workload: Idle (Win 7)                                                                       |      |

| Table 41: Workload: Typical                                                                            |      |

| Table 42: Workload: Maximum                                                                            |      |

| Table 43: Power Consumption of CP6007-SA Accessories                                                   |      |

| Table 44: Power Consumption per Gigabit Ethernet Port                                                  |      |

| Table 45: PMC Module Current                                                                           |      |

| Table 45: PMC Module Current                                                                           |      |

| Table 45: XMC Module Current                                                                           |      |

|                                                                                                        |      |

| Table 48: Main Setup Menu Functions                                                                    |      |

| Table 49: Advanced Setup Menu Sub-Screens and Functions                                                |      |

| Table 50: Security Setup Menu Functions                                                                |      |

| Table 51: Boot Priority Order                                                                          |      |

| Table 52: Exit Setup Menu Functions                                                                    |      |

| Table 53: Kontron-Specific uEFI Shell Commands                                                         |      |

| Table 54: Standard IPMI Commands                                                                       |      |

| Table 55: Supported PICMG Commands                                                                     |      |

| Table 56: Get Device ID Command                                                                        |      |

| Table 57: Sensor List                                                                                  |      |

| Table 58: Thresholds – Standard Temperature Range (CP6007-SA) and Extended Temperature Range (CP6007-I |      |

| Table 59: Voltage Sensor Thresholds                                                                    |      |

| Table 60: OEM Event/Reading Types                                                                      |      |

| Table 61: List of Acronyms                                                                             | .102 |

## List of Figures

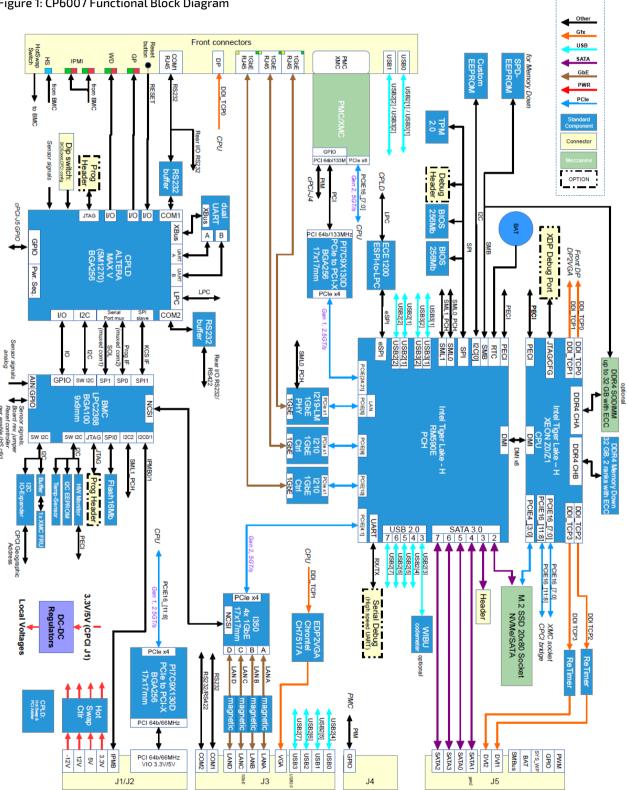

| Figure 1: CP6007 Functional Block Diagram                                                                 | 16 |

|-----------------------------------------------------------------------------------------------------------|----|

| Figure 2: 4 HP CP6007 Front Panel                                                                         | 17 |

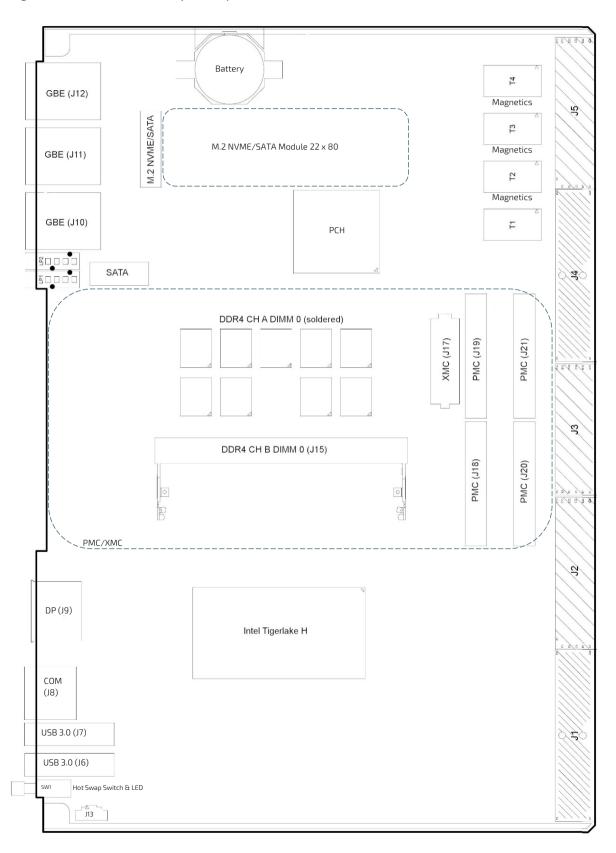

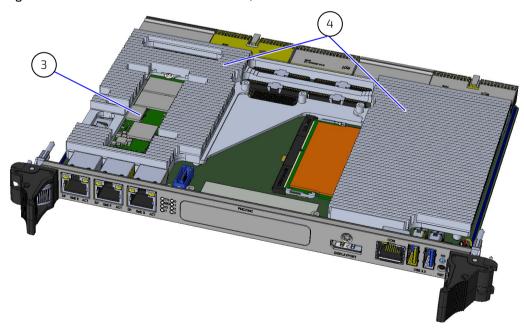

| Figure 3: 4 HP CP6007 Board Layout (Top View)                                                             | 18 |

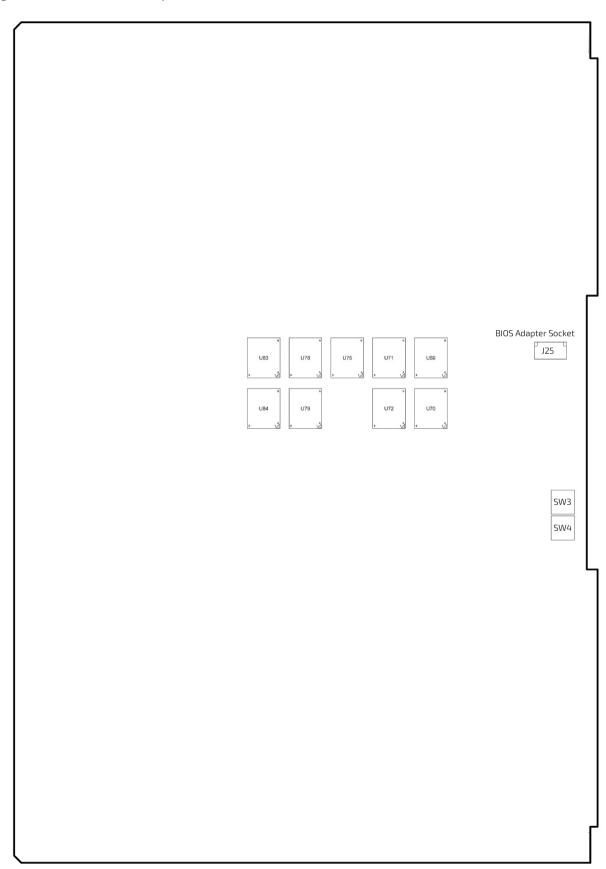

| Figure 4: 4 HP CP6007 Board Layout (Bottom View)                                                          | 19 |

| Figure 5: Serial Port Connect or J8                                                                       | 34 |

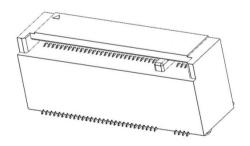

| Figure 6: M.2 Connector                                                                                   | 36 |

| Figure 7: Compact PCI Connectors                                                                          | 40 |

| Figure 8: Location of DIP Switch SW3 and SW4                                                              | 50 |

| Figure 9: Ambient Temperature for Xeon® W-11865MRE, measured by Intel PTU Tool for Broadwell-DE rev. 1.1  | 65 |

| Figure 10: Ambient Temperature for Xeon® W-11555MRE, measured by Intel PTU Tool for Broadwell-DE rev. 1.1 | 66 |

| Figure 11: CP6007-SA with M.2 card and heat sink installed                                                | 70 |

| Figure 12: CP6007-RA with M.2 card installed, without heat sink                                           |    |

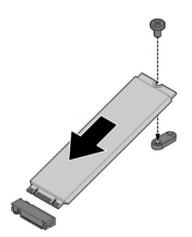

| Figure 13: Installing a M.2 Card                                                                          |    |

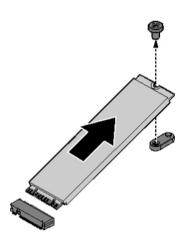

| Figure 14: Removing a M.2 Card                                                                            | 72 |

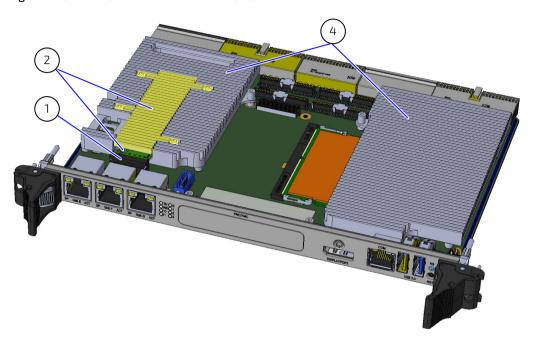

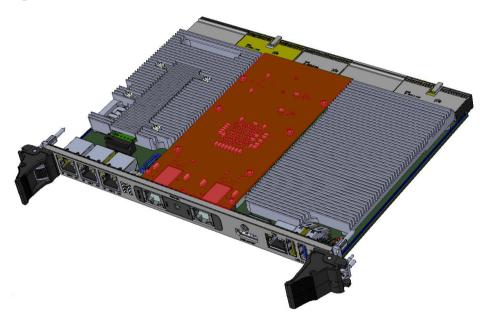

| Figure 15: CP6007-SA with PMC/XMC Module installed (marked red)                                           | 73 |

### 1/ Introduction

#### 1.1. Board Overview

CP6007-SA is based on Intel's 11th Gen Xeon® processors with 10nm technology, with outstanding performance-perwatt values. Its scalable power budget allows users to tailor the power dissipation to their requirements. CP6007 is well suited for general computing and as well for advanced Multi-CPU server applications, built as virtual machines and based on PICMG2.16. By using virtualization, any CP6007 based platform becomes a future proof investment.

CP6007 comes in two variants, standard air-cooled CP6007-SA and rugged air-cooled CP6007-RA. CP6007-SA is designed for rather standard environments from  $0^{\circ}$ C to  $+60^{\circ}$ C, featured by up to 64GB memory with Error Correction Code (ECC) support. CP6007-RA is designed for harsh air-cooled environments, following VITA47 with high shock and vibration demands and temperature ranges from  $-40^{\circ}$ C to  $+70^{\circ}$ C. CP6007-RA is equipped with 32 GB soldered memory.

CP6007 is featured by a rich selection of communication and media interfaces. A Trusted Platform Module (TPM 2.0) stands for enhanced hardware and software based data and system security. CP6007 is prepared to operate with different storage devices: onboard industrial grade M.2 flash devices, NVMe as well as SATA, or 2.5 inch SATA hard disk or SSD to be placed on a respective rear-I/O module. CP6007 also features an XMC site according to VITA 42.3 (XMC1.0) supporting x8 PCI Express®, and alternatively a PMC site, for various market available extensions. Based on the Kontron rear I/O concept, the rear I/O transition module series is fully functional with CP6007-SA.

CP6007 is widely backward compatibility to earlier Kontron blades. The well-established CompactPCI® eco system, combined with a long availability of the 11th Gen Intel® Xeon® processor family, and Kontron's reliable technical support, make CP6007-SA a safe choice.

The board is offered with various board support packages including Windows and Linux operating systems. For further information concerning the operating systems available for the CP6007, please contact Kontron.

### 1.2. System Expansion Capabilities

#### 1.2.1. PMC Module

The CP6007 has a 3.3 V, PMC mezzanine interface configurable for 64-bit / 66 MHz PCI operation. This interface supports a wide range of PMC modules with PCI interface including all of Kontron's PMC modules and provides an easy and flexible way to configure the CP6007 for various application requirements. For information on the PMC interface, refer to Chapter 2.7.7, "PMC Interface".

#### 1.2.2. XMC Module

The CP6007 has one XMC mezzanine interface for support of x1, x4 and x8 PCI Express 2.0 XMC modules providing an easy and flexible way to configure the CP6007 for various application requirements. For information on the XMC interface, refer to Chapter 2.7.8, "XMC Interface".

#### 1.2.3. Rear I/O Module

The CP6007 provides support for one rear I/O module via the CompactPCI rear I/O connectors. For further information refer to 2.7.10 "CompactPCI Interface".

## 1.2.4. M.2 Storage

CP6007 provides support for SATA/NVMe SSD Flash memory in combination with an optional M.2 storage device, connected to a respective onboard connector. Market available M.2 devices of suitable size and keying currently provide storage capacities of 32 GB up to 1 TB. For further information about the M.2 Flash module, refer to Chapter 2.7.6 "SATA Interfaces" and 2.7.7 "M.2 Socket".

## 1.3. Board Diagrams

The following diagrams provide additional information concerning board functionality and component layout.

## 1.3.1. Functional Block Diagram

Figure 1: CP6007 Functional Block Diagram

//16 www.kontron.com

#### 1.3.2. Front Panel

Figure 2: 4 HP CP6007 Front Panel

#### **IPMI LEDs**

10/I1 (red/green): Indicate the software status of the IPMI controller

#### System Status LEDs

HS (blue): Hot Swap Status

TH (red/green): Temperature Status

WD (green): Watchdog Status

#### General Purpose LEDs

LED3-0 (red/green/amber): General Purpose / POST Code

Note: If the General Purpose LEDs 3–0 are lit red during boot-up,

a failure is indicated before the uEFI BIOS has started.

## Integral Ethernet LEDs

ACT (green): Ethernet Link/Activity

SPEED (orange): 1000BASE-T Ethernet Speed

SPEED (green): 100BASE-TX Ethernet Speed

SPEED (off) + ACT (on): 10BASE-T Ethernet Speed

## 1.3.3. Board Layout

Figure 3: 4 HP CP6007 Board Layout (Top View)

Figure 4: 4 HP CP6007 Board Layout (Bottom View)

## 1.4. Technical Specification

Table 1: CP6007 Main Specifications

| Processor & Chipset |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor           | The CP6007 supports the following 11th Gen Intel® Xeon® processors:  W-11555MRE, 6 core, 12 MByte cache, 2.6 GHz 45 W (TDP), 2.1 GHz 35 W (cTDP)  W-11865MRE, 8 core, 24 MByte cache, 2.6 GHz 45 W (TDP), 2.1 GHz 35 W (cTDP)  Chipset RM590E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Memory              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| System Memory       | <ul> <li>32 GByte soldered RAM with ECC and data speed of up to 3200 MHz</li> <li>CP6007-SA only: 32 GByte SODIMM as additional option, dual channel DDR4 with ECC, up to 3200 MHz</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Flash Memory        | <ul><li>Sockets NVMe and SATA for alternative use, for M.2 2280 Solid State Drive</li><li>Two redundant 32 MByte SPI Flashes</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| EEPROM              | EEPROM with 64 kbit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interfaces          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CompactPCI          | Compliant with CompactPCI Specification PICMG 2.0 Rev. 3.0:  System controller operation  64-bit / 66 MHz PCI or PCI-X master interface with dedicated PCIe-to-PCI-X bridge  3.3V or 5V signaling levels (universal signaling support)  Compliant with the Packet Switching Specification PICMG 2.16  The CP6007 supports System Master hot swap functionality and application-dependent hot swap functionality when used in a peripheral slot.  When used as a System Master, the CP6007 supports individual clocks for each slot and the ENUM signal handling is in compliance with the PICMG 2.1 Hot Swap Specification.  When installed in a peripheral slot, the CP6007 is isolated from the CompactPCI bus. It receives power from the backplane and supports rear I/O and, if the system supports it, packet switching (in this case up to two channels of Gigabit Ethernet). |

| Standard Rear I/O   | The following interfaces are routed to the rear I/O connectors J3, J4 and J5.  COMA (RS-232 signaling) and COMB (RS-232/RS-422 signaling); no buffer on the rear I/O module is necessary  4 x USB 2.0  1 x CRT VGA, 2 x DVI/HDMI  2 x Gigabit Ethernet (compliant with PICMG 2.16, R 1.0)  CP6007-RA: 2 additional GbE (J3)  4 x SATA 3 Gb/s (up to)  4 x GPIs and 4 GPOs (LVTTL signaling)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

<u>www.kontron.com</u> // 20

| Interfaces       |                                                                                                                                                                                                                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gigabit Ethernet | CP6007-SA  Five 10 Base-T/100 Base-TX/1000 Base-T Gigabit Ethernet interfaces based on two Intel® I210-IT Gigabit Ethernet controllers, one Intel® I219 Gigabit Ethernet controller and one Intel® I350 quad-port Gigabit Ethernet controller (only two ports used):  Three RJ-45 connectors on the front panel  Two ports on the rear I/O (PICMG 2.16) |

| Gigabit Ethernet | CP6007-RA  Seven 10 Base-T/100 Base-TX/1000 Base-T Gigabit Ethernet interfaces based on two Intel® I210-IT Gigabit Ethernet controller, one Intel® I219 Gigabit Ethernet controller and one Intel® I350 quad-port Gigabit Ethernet controller:  Three RJ-45 connectors on the front panel  Four ports on the rear I/O (PICMG 2.16)                      |

| USB              | Six USB ports supporting UHCI (USB 1.1), EHCI (USB 2.0) and XHCI (USB 3.0):  Two type A USB 3.0 connectors on the front panel  Four USB 2.0 ports on the rear I/O interface                                                                                                                                                                             |

| Serial           | Two 16C550-compatible UARTs:  One RS-232 port on the front panel and routed to rear I/O, COM1  One RS-232/RS-422 port on the rear I/O, COM2                                                                                                                                                                                                             |

| PMC/XMC          | One 64-bit / 66 MHz PMC slot, Pn1-Pn4, 3.3 volt V(I/O) Alternatively one XMC slot via J17, supporting VITA 42.3 (PCIe Gen3 x 8)                                                                                                                                                                                                                         |

| SATA             | Four ports to rear I/O (SATA 3Gb/s) One standard SATA 6Gb/s connector One mounting option for M.2 2280 SSD flash (SATA 6Gb/s)                                                                                                                                                                                                                           |

| Sockets                |                                                                                                                                                                                                                                                        |  |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Front Panel Connectors | DisplayPort: one DP connector, J9                                                                                                                                                                                                                      |  |

|                        | USB: two 4-pin, type A connectors, J6 and J7                                                                                                                                                                                                           |  |

|                        | Ethernet: three 8-pin, RJ-45 connectors, J10, J11 and J12                                                                                                                                                                                              |  |

|                        | Serial port: one 8-pin, RJ-45 connector, J8 (COMA)                                                                                                                                                                                                     |  |

|                        | XMC front panel bezel cutout                                                                                                                                                                                                                           |  |

| 01                     |                                                                                                                                                                                                                                                        |  |

| Onboard Connectors     | One XMC connector, J17                                                                                                                                                                                                                                 |  |

|                        | One M.2 socket (J18) with SATA 6 Gb/s and NVMe (PCIe Gen3 x4) Interface                                                                                                                                                                                |  |

|                        | One 7-pin, standard SATA 6 Gb/s connector, J14                                                                                                                                                                                                         |  |

|                        | Four PMC connectors J18, J19, J20 J21                                                                                                                                                                                                                  |  |

|                        | Five CompactPCI connectors J1, J2, J3, J4 and J5                                                                                                                                                                                                       |  |

|                        | One soldered DDR4 memory bank                                                                                                                                                                                                                          |  |

|                        | (CP6007-SA: one additional DDR4 SODIMM socket J15)                                                                                                                                                                                                     |  |

| LEDs                   |                                                                                                                                                                                                                                                        |  |

| Front Panel LEDs       | IPMI LEDs:                                                                                                                                                                                                                                             |  |

|                        | ▶ IO/I1 (red/green): Software status of the IPMI controller                                                                                                                                                                                            |  |

|                        | System Status LEDs:                                                                                                                                                                                                                                    |  |

|                        | WD (green): Watchdog status                                                                                                                                                                                                                            |  |

|                        | TH (red/green): Temperature status                                                                                                                                                                                                                     |  |

|                        | HS (blue): Hot swap status                                                                                                                                                                                                                             |  |

|                        | General Purpose LEDs:                                                                                                                                                                                                                                  |  |

|                        | LED3-0 (red/green/amber): General purpose / POST code                                                                                                                                                                                                  |  |

|                        | Ethernet LEDs:                                                                                                                                                                                                                                         |  |

|                        | ACT (green): Network link / activity                                                                                                                                                                                                                   |  |

|                        | SPEED (green/orange): Network speed                                                                                                                                                                                                                    |  |

| Switches               |                                                                                                                                                                                                                                                        |  |

| DIP Switches           | Two onboard DIP switches, SW3 and SW4 for board configuration on the rear side of the board                                                                                                                                                            |  |

| Reset Switch           | One hardware reset switch on the front panel                                                                                                                                                                                                           |  |

| Hot Swap Switch        | One switch for hot swap purposes integrated in the front panel in accordance with PICMG 2.1 Rev. 2.0                                                                                                                                                   |  |

| Timer                  |                                                                                                                                                                                                                                                        |  |

| Real-Time Clock        | Real-time clock with 256 Byte CMOS RAM; battery-backup available                                                                                                                                                                                       |  |

| Watchdog Timer         | Software-configurable, two-stage Watchdog with programmable timeout ranging from 125 ms to 4096 s in 16 steps                                                                                                                                          |  |

|                        | Serves for generating IRQ or hardware reset                                                                                                                                                                                                            |  |

| System Timer           | The Intel® SoC contains three 8254-style counters with fixed uses.                                                                                                                                                                                     |  |

|                        | In addition to the three 8254-style counters, the Intel® SoC includes eight individual high-precision event timers that may be used by the operating system. They are implemented as a single counter each with its own comparator and value register. |  |

| IPMI               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPMI Controller    | NXP® ARM7 microcontroller with 512 kB firmware flash and automatic rollback strategy  The IPMI controller carries out IPMI commands such as monitoring several onboard temperature conditions, board voltages and the power supply status, and managing hot swap operations.  The IPMI controller is accessible via two IPMBs, one host Keyboard Controller Style (KCS) Interface and up to four Gigabit Ethernet Interfaces (IOL).                                                                                                            |

| Thermal            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Thermal Management | <ul> <li>CPU and board overtemperature protection is provided by:</li> <li>Temperature sensors integrated in the Intel® SoC:</li> <li>One temperature sensor for monitoring each processor core</li> <li>One temperature sensor for monitoring the package die temperature</li> <li>One onboard temperature sensor for monitoring the board temperature</li> <li>Specially designed heat sink</li> </ul>                                                                                                                                       |

| Security           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TPM                | Trusted Platform Module (TPM) 2.0 for enhanced hardware- and software-based data and system security                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Software           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| uEFI BIOS          | <ul> <li>AMI Aptio V™ BIOS firmware based on the uEFI Specification and the Intel Platform Innovation Framework for EFI:</li> <li>LAN boot capability for diskless systems (UEFI Networks Stack)</li> <li>(OPEN) Automatic fail-safe recovery in case of a damaged image</li> <li>Non-volatile storage of setup settings in the SPI boot flash (battery only required for the RTC)</li> <li>Command shell for diagnostics</li> <li>uEFI Shell commands executable from mass storage device in a pre-OS environment (open interface)</li> </ul> |

| Software (continued)                                                                                       |                                                                                                                                                    |  |

|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IPMI Firmware   IPMI firmware providing the following features:                                            |                                                                                                                                                    |  |

|                                                                                                            | Keyboard Controller Style (KCS) interface                                                                                                          |  |

|                                                                                                            | Dual-port IPMB interface for out-of-band management and sensor monitoring                                                                          |  |

|                                                                                                            | IPMI over LAN (IOL) and Serial over LAN (SOL) support                                                                                              |  |

|                                                                                                            | Sensor Device functionality with configurable thresholds for monitoring board<br>voltages, CPU state, board reset, etc.                            |  |

|                                                                                                            | FRU Inventory functionality                                                                                                                        |  |

| System Event Log (SEL), Event Receiver functionalities  Sensor Data Record Repository (SDRR) functionality |                                                                                                                                                    |  |

|                                                                                                            |                                                                                                                                                    |  |

|                                                                                                            | Board monitoring and control extensions:                                                                                                           |  |

|                                                                                                            | <ul> <li>Graceful shutdown support</li> <li>(OPEN) uEFI BIOS fail-over control: selection of the SPI boot flash<br/>(standard/recovery)</li> </ul> |  |

|                                                                                                            | Field-upgradeable IPMI firmware:                                                                                                                   |  |

|                                                                                                            | via the KCS, IPMB or IOL interfaces                                                                                                                |  |

|                                                                                                            | <ul> <li>Download of firmware does not break the currently running firmware or<br/>payload activities</li> </ul>                                   |  |

|                                                                                                            | Two flash banks with rollback capability: manual rollback or automatic in case of<br>upgrade failure                                               |  |

| Operating Systems                                                                                          | There are various operating systems available for the CP6007. For further information, please contact Kontron.                                     |  |

| General                                                                                                    | '                                                                                                                                                  |  |

| Power Consumption                                                                                          | See Chapter 4 for details.                                                                                                                         |  |

| MTBF                                                                                                       | 110000 hrs acc. to MIL-HDBK-217 FN2 Ground Benign 30 °                                                                                             |  |

| Temperature Range                                                                                          | Operational:                                                                                                                                       |  |

|                                                                                                            | 0 °C to 60 °C Standard (CP6007-SA)                                                                                                                 |  |

|                                                                                                            | -40 °C to +70 °C Extended (CP6007-RA),                                                                                                             |  |

|                                                                                                            | passive module heat sink, requires forced airflow cooling.                                                                                         |  |

|                                                                                                            | Storage:                                                                                                                                           |  |

|                                                                                                            | -55 °C to +85 °C (without hard disk and without battery)                                                                                           |  |

| Battery                                                                                                    | 3.0 V lithium battery for RTC with battery socket Battery type: UL-approved CR2025                                                                 |  |

|                                                                                                            | Temperature ranges:                                                                                                                                |  |

|                                                                                                            | Operational (load): -20 °C to +70 °C typical (refer to the battery manufacturer's specifications for exact range)                                  |  |

|                                                                                                            | Storage (no load): -40 °C to +70 °C typical                                                                                                        |  |

| Climatic Humidity                                                                                          | 93% RH at 40 °C, non-condensing (acc. to IEC 60068-2-78)                                                                                           |  |

| Dimensions                                                                                                 | 233.35 mm x 160 mm                                                                                                                                 |  |

|                                                                                                            | 6U, 4 HP, CompactPCI Serial-compliant form factor (6U, 8HP with 4-DIMM option)                                                                     |  |

| Board Weight                                                                                               | CP6007-SA with heat sink: approx. 900 grams                                                                                                        |  |

| -                                                                                                          | CP6007-RA with heat sink: approx. 900 grams                                                                                                        |  |

|                                                                                                            | The above-mentioned board weight refers to the CP6007 without extension modules (XMC, PMC)                                                         |  |

## 1.5. Compliance

This product complies with the requirements of the following standards.

Table 2: Environmental Conditions and Compliance

| Operating Temperature Storage   | -0°C to +60°C  Some connectors and supercap has operating temperature only 0°C to +70°C, relative humidity (non-condensing) 10 % to 93 % at 40°C  -30°C to +85°C                                                                                   |                    |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Temperature                     | relative humidity (non-condensing) 10 % to 93 % at 40°C                                                                                                                                                                                            |                    |

| Compliance                      | CE/UKCA, RoHS II, WEEE                                                                                                                                                                                                                             |                    |

| CP6007-SA                       |                                                                                                                                                                                                                                                    |                    |

| Vibration<br>(Sinusoidal)       | 10-300 Hz frequency range<br>2 g acceleration<br>1 oct/min sweep rate<br>10 cycles/axis, 3 axes                                                                                                                                                    | EN600068-2-6:2008  |

| Single Shock                    | 30 g acceleration<br>9 ms shock duration; half sine<br>3 impacts per direction (total 18), 3 s recovery time                                                                                                                                       | EN60068-2-27:2010  |

| Permanent Shock                 | 15 g acceleration<br>11 ms shock duration; half sine<br>500 impacts per direction (total 3000), 1 s recovery<br>time                                                                                                                               | EN60068-2-27:2010  |

| CP6007-RA                       |                                                                                                                                                                                                                                                    |                    |

| Random Vibration<br>(Broadband) | Test parameters according to ANSI/VITA 47 Class V2<br>5 - 100 Hz frequency range: +3dB/Oct.<br>100 - 1000 Hz freq. range 0.04 g²/Hz<br>1000 - 2000 Hz freq. range: -6dB/Oct.<br>effective value: 7.62 g rms<br>30 min test duration / axis, 3 axes | EN600068-2-64:2020 |

| Single Shock                    | Test parameters according to ANSI/VITA 47 Class OS1 20 g acceleration 11 ms shock duration; half sine 3 impacts per direction (total 18) 3 s recovery time                                                                                         | EN60068-2-27:2010  |

| Permanent Shock                 | 15 g acceleration<br>11 ms shock duration; half sine<br>500 impacts per direction (total 3000)<br>1 s recovery time                                                                                                                                | EN60068-2-27:2010  |

## **NOTICE**

Customers desiring to perform further environmental testing of the CP6007 must contact Kontron for assistance prior to performing any such testing.

Boards without conformal coating must not be exposed to a change of temperature which can lead to condensation. Condensation may cause irreversible damage, especially when the board is powered up again.

Kontron does not accept any responsibility for damage to products resulting from destructive environmental testing

## 1.6. Related Publications

The following publications contain information relating to this product.

Table 3: Related Publications

| Product                                                                                              | Publication                                                                |

|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| CompactPCI Systems                                                                                   | PICMG 2.0, Rev. 3.0 CompactPCI Specification                               |