| Related Products | MOPS/386A (P389)                  |

|------------------|-----------------------------------|

| Subject          | I <sup>2</sup> C bus on MOPS/386A |

| Document Name    | I2CP389_E210.doc                  |

| Usage            | Common                            |

## 1. REVISION HISTORY

| Date      | Document Name | Subjects added, changed, deleted    | Changed by |

|-----------|---------------|-------------------------------------|------------|

| 18-Dec-02 | I2CP389_E210  | Initial release of Application Note | H. Bruhn   |

|           |               |                                     |            |

|           |               |                                     |            |

#### 2. TABLE OF CONTENTS

| 1.   | REVISION HISTORY                                             | 1 |

|------|--------------------------------------------------------------|---|

| 2.   | TABLE OF CONTENTS                                            | 2 |

| 3.   | GENERAL INFORMATION ABOUT I <sup>2</sup> C BUS               | 3 |

| 3.1. | Introduction to I <sup>2</sup> C Bus                         | 3 |

| 3.2. | I <sup>2</sup> C Bus on Kontron Embedded Modules GmbH Boards | 4 |

| 4.   | ACCESS TO I <sup>2</sup> C BUS ON MOPS/386A                  | 5 |

| 4.1. | Schematics                                                   | 5 |

| 4.2. | Used I <sup>2</sup> C bus addresses                          | 5 |

| 4.3. | Programming information                                      | 6 |

## 3. GENERAL INFORMATION ABOUT I<sup>2</sup>C BUS

#### 3.1. Introduction to I<sup>2</sup>C Bus

The Inter-IC bus ( $I^2C$ ) is a two-wired serial bus and provides a sort of small area network between the circuits of one system and between different systems. Any device with built-in  $I^2C$  bus interface can be connected to the system by simply clipping it to the  $I^2C$  bus. It consists of two bi-directional lines for serial data (I2DAT) and serial clock (I2CLK). Every device connected can be master or slave, so there is no central master. A device addressed as a slave during one data transfer could possibly be the master for the next data transfer. Devices are also free to transmit or receive data during a transfer. The inherent synchronization process in connection with the wired AND technique allows fast devices to communicate with slower ones.

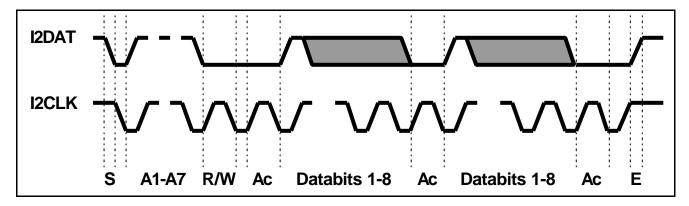

For each data bit transferred one clock pulse has to be generated. The data on the I2DAT line must be stable during the high period of the clock. The data lines state can only change when the I2CLK line is low. Data transfer is entered by a start condition and ended by a stop condition. A high to low transition of the I2DAT line, while the I2CLK is high, signals the start condition and a low to high transition, while I2CLK is high, indicates the stop-condition. Data transfer follows the format below:

After the start condition (S) the slave address byte is sent. This byte consists of seven address bits (A1-A7) and one direction bit (R/W) with low level indicating a transmission (WRITE) and high level indicating a request for data (READ).

After the addressing of a slave device the master's next clock pulse is used for acknowledgement (Ac). During this acknowledge pulse the I2DAT line has to be pulled down to low by the receiving device. A data transfer is always terminated by a stop condition (E) generated by the master. However, if the master wants to communicate with another device on the bus it generates another start condition to address another slave without the necessity of first generating a stop condition.

This was only a short summary concerning the  $l^2C$  bus. For detailed information (e.g. timing problems, characteristics of devices) refer to  $l^2C$  bus specifications, data books and specialized textbooks.

#### 3.2. I<sup>2</sup>C Bus on Kontron Embedded Modules GmbH Boards

The  $l^2C$  bus interface on **Kontron Embedded Modules GmbH** boards has to be implemented by the customer via software, which drives the two lines I2DAT and I2CLK, following the  $l^2C$  bus specifications. The basic hardware to design the software interface is standard on the devices mentioned in this application note.

#### Note: This kind of interface does not support external masters.

On different **Kontron Embedded Modules GmbH** boards the two  $I^2C$  bus lines are not offered on identical connectors. They are also not driven the same way. Refer to your manual if you're not sure you're using the right connector or pins for your  $I^2C$  application.

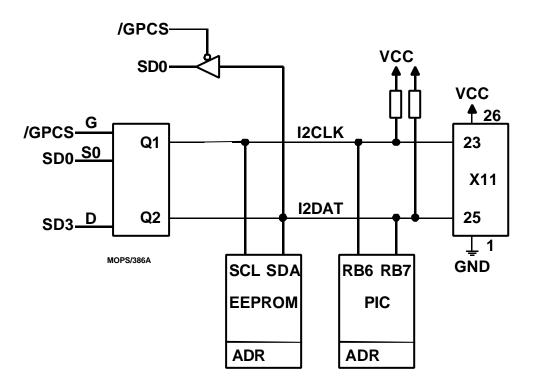

The following schematics show the bus interface and the onboard devices connected to the  $^{2}C$  bus on the special **Kontron** board the application note is related to. Therefore the information herein cannot be used for other products of **Kontron**.

## 4. ACCESS TO I<sup>2</sup>C BUS ON MOPS/386A

#### 4.1. Schematics

The signal line SD0 selects the I2CLK or I2DAT line for output. The signal line SD3 holds the "data", when set to 0 the selected line I2CLK or I2DAT is pulled LOW.

## 4.2. Used I<sup>2</sup>C bus addresses

I/O address to generate /CS : 51h

| Device address of EEPROM   | : | 1010 000xb |

|----------------------------|---|------------|

| Device address of PIC16F84 | : | 0101 101xb |

| Device address of MAX517   | : | 0101 100xb |

<u>Attention:</u> These devices are for BIOS-access only; reading from or writing to them may cause data corruption and system failure.

#### **Programming information** 4.3.

First of all it is good to define some global constant values, which can be used by the functions later on.

| CTL_REG_1      | EQU | 051h ; control port address                                    |

|----------------|-----|----------------------------------------------------------------|

| PORT61         | EQU | 061h ; XT port 61hex                                           |

| REFRESH_STATUS | EQU | 010h ; Refresh status bit port 61hex                           |

| 12DAT_HIGH     | EQU | ((0  shl  0) + (1  shl  3)); bit 0 set to 0 and bit 3 set to 1 |

| I2DAT_LOW      | EQU | ((0  shl  0) + (0  shl  3)); bit 0 set to 0 and bit 3 set to 0 |

| 12CLK_HIGH     | EQU | ((0  shl  0) + (1  shl  3)); bit 1 set to 0 and bit 3 set to 1 |

| I2CLK_LOW      | EQU | ((0 shl 0) + (0 shl 3)); bit 1 set to 0 and bit 3 set to 0     |

Here are the functions for driving the  $l^2C$  lines.

| ; Name:<br>;<br>;<br>;                       | I2cSclLow<br>I2cSclHigh<br>I2cSdaLow<br>I2cSdaHigh - functions for driving the I2C lines |

|----------------------------------------------|------------------------------------------------------------------------------------------|

| ; Modified:                                  | none<br>none<br>destroy AX and minor flags                                               |

| mov                                          | PROC NEAR PUBLIC<br>al, I2CLK_LOW<br>CTL_REG_1, al<br>ENDP                               |

| I2cSclHigh<br>mov<br>out<br>ret<br>I2cSclLow | PROC NEAR PUBLIC<br>al, I2CLK_HIGH<br>CTL_REG_1, al<br>ENDP                              |

| I2cSdaLow<br>mov<br>out<br>ret<br>I2cSclLow  | PROC NEAR PUBLIC<br>al, I2DAT_LOW<br>CTL_REG_1, al<br>ENDP                               |

| I2cSdaHigh<br>mov<br>out<br>ret<br>I2cSclLow | PROC NEAR PUBLIC<br>al, I2DAT_HIGH<br>CTL_REG_1, al<br>ENDP                              |

Here is the function to read the current status of the  $l^2C$  data line.

```

; -

; Name:

I2cReadSda

; Entry:

none

; Exit:

none

; Modified: destroy AX and minor flags

; -

I2cReadSda PROC NEAR PUBLIC

in al, CTL_REG_1

and al, 001h

ret

I2cReadSda ENDP

```

# **Application Note**

True  $^{2}C$  bus devices allow a maximum speed of 100KHz. Therefore it is necessary to have a delay when driving the  $l^{2}C$  bus. The following function offers a delay by number of 15 microsecond periods. This function should not be called with 0 in CX. The entry value in CX therefore should be minimum 1. For the Kontron onboard devices we recommend a value of 5 in CX which results in a clock delay of 75 microseconds.

However, there are many devices with m fC interface on the market that may not allow a speed of 100KHz. Please read the datasheet of your m fC device very carefully to find out the I2CLK delay. Use a suitable entry value in CX to call this function for your device.

```

; Name:

FixedDelav

; Entry:

CX - Time in 15us (DO NOT CALL with CX==0 or CX>0FFF8h !!!)

; Exit:

none

; Modified: CX and flags

;------

_____

FixedDelay PROC NEAR PUBLIC

pusha

pushf

ah, NOT(REFRESH_STATUS)

mov

; force ah, al miscompare

add

cx, 2

loopSampleRefresh:

; I/O delay

icxz $+2

al, PORT61

; load port 61hex status

in

and

al, REFRESH_STATUS

; isolate refresh status

; match last status?

cmp

al, ah

loopSampleRefresh

; yes-loop if hasn't toggled

ie

saveStatus:

mov

ah, al

; save new state of refresh status

loop loopSampleRefresh

; repeat until timer expires

popf

popa

ret

FixedDelay ENDP

```

The MOPS/386A has an onboard keyboard matrix PIC which uses the lines I2CLK and I2DAT as matrix scan lines, too. Therefore it is necessary to stop the PIC from driving and scanning the keyboard matrix interface, thus freeing the  $I^2C$  bus.

This must be done by holding the data line I2DAT low for at least 60 microseconds to ensure that the keyboard matrix PIC recognizes the  $l^2$ C bus arbitration and stops scanning.

The PIC will start the matrix scan again after five millisceconds of no action on the  $I^2C$  bus.

The following function does the necessary bus arbitration and has to be called whenever a transfer of data to a device on the fC bus has to be done.

```

;-----

_____

; Name:

I2cArbit

; Entry:

none

; Exit:

none

; Modified: may change AX, DX and flags

_____

;------

bit PROC NEAR PUBLIC

call I2cSdaLow

I2cArbit

; force I2DAT low

push cx

cx, (60/15)+1

; 60 microseconds delay

mov

call FixedDelay

сx

pop

call I2cSdaHigh

; release I2DAT

ret

I2cArbit

ENDP

```