# Intel<sup>®</sup> Server Board S5000PHB

**Technical Product Specification**

*April 2008* Rev. 1.2

Order Number: D70057-005

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The Intel<sup>®</sup> Server Board S5000PHB may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium Inside, skool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2008, Intel Corporation. All Rights Reserved.

# Contents

| 1 | <b>Intro</b><br>1.1<br>1.2 | oduction                                                                                             |

|---|----------------------------|------------------------------------------------------------------------------------------------------|

| - |                            |                                                                                                      |

| 2 |                            | luct Overview                                                                                        |

|   | 2.1<br>2.2                 | Intel <sup>®</sup> Server Board S5000PHB SKU Availability                                            |

|   | 2.2                        | Server Board Layout                                                                                  |

|   | 2.5                        | 2.3.1 Connector and Component Locations                                                              |

|   |                            | 2.3.2 Light Guided Diagnostic LED Locations                                                          |

|   |                            | 2.3.3 Server Board Mechanical Drawings                                                               |

| 2 | Fund                       | C C                                                                                                  |

| 3 |                            | 17                                                                                                   |

|   | 3.1<br>3.2                 | Block Diagrams                                                                                       |

|   | 3.2                        | Intel® 5000P Memory Controller Hub (MCH)213.2.1System Bus Interface                                  |

|   |                            | 3.2.2 Processor Support                                                                              |

|   |                            | 3.2.2.1 Processor Population Rules                                                                   |

|   |                            | 3.2.2.2 Common Enabling Kit (CEK) Design Support                                                     |

|   |                            | 3.2.3 Memory Sub-system                                                                              |

|   |                            | 3.2.3.1 Memory RASUM Features                                                                        |

|   |                            | 3.2.3.2 Supported Memory                                                                             |

|   |                            | 3.2.3.3 DIMM Population Rules and Supported DIMM Configurations                                      |

|   | 3.3                        | ESB2-E I/O Controller                                                                                |

|   |                            | 3.3.1 PCI Sub-System                                                                                 |

|   |                            | 3.3.1.1 PCI32: 32-bit, 33-MHz PCI Subsystem                                                          |

|   |                            | 3.3.1.2 PXA: 64-bit, 133MHz PCI Subsystem                                                            |

|   |                            | 3.3.1.4 PE4: One x4 PCI Express Bus Segment                                                          |

|   |                            | 3.3.1.5 PE6, PE7: Two x4 PCI Express Bus Segments                                                    |

|   |                            | 3.3.1.6 PCI Riser Slot                                                                               |

|   |                            | 3.3.2 Parallel ATA (PATA) Support26                                                                  |

|   |                            | 3.3.3 USB 2.0 Support                                                                                |

|   | 3.4                        | Video Support                                                                                        |

|   |                            | 3.4.1 Video Modes                                                                                    |

|   |                            | 3.4.2 Video Memory Interface                                                                         |

|   | o =                        | 3.4.3 Dual Video                                                                                     |

|   | 3.5                        | Network Interface Controller (NIC)                                                                   |

|   |                            | 3.5.1       I/O Acceleration Technology       29         3.5.2       MAC Address Definition       30 |

|   | 3.6                        | Super I/O Device                                                                                     |

|   | 3.0                        | 3.6.1 Serial Ports                                                                                   |

|   |                            | 3.6.1.1 Serial Port B                                                                                |

|   |                            | 3.6.1.2 Serial Port A                                                                                |

|   |                            | 3.6.2 Floppy Disk Controller                                                                         |

|   |                            | 3.6.3 Keyboard and Mouse Support                                                                     |

|   |                            | 3.6.4 Wake-up Control                                                                                |

|   |                            | 3.6.5 System Health Support 32                                                                       |

| 4 | Platf                      | form Management                                                                                      |

| 5 | Conr                       | nector / Header Locations and Pin-outs                                                               |

|   | 5.1                        | Board Connector Information                                                                          |

|   | 5.2                        | Power Connectors                                                                                     |

|   | 5.3                                     | System                                                                                                                                                                                                                                                                                                            | Management Headers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                             |

|---|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|   |                                         | 5.3.1                                                                                                                                                                                                                                                                                                             | Remote Management Module 2 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                             |

|   |                                         | 5.3.2                                                                                                                                                                                                                                                                                                             | IPMB Header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 37                                                                                          |

|   | 5.4                                     | Riser Su                                                                                                                                                                                                                                                                                                          | uperslot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37                                                                                          |

|   | 5.5                                     | Front Pa                                                                                                                                                                                                                                                                                                          | anel Flex Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41                                                                                          |

|   | 5.6                                     | I/O Cor                                                                                                                                                                                                                                                                                                           | nnector Pinout Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43                                                                                          |

|   |                                         | 5.6.1                                                                                                                                                                                                                                                                                                             | VGA Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 43                                                                                          |

|   |                                         | 5.6.2                                                                                                                                                                                                                                                                                                             | NIC Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                                          |

|   |                                         | 5.6.3                                                                                                                                                                                                                                                                                                             | IDE Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44                                                                                          |

|   |                                         | 5.6.4                                                                                                                                                                                                                                                                                                             | GCM3 Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 45                                                                                          |

|   |                                         | 5.6.5                                                                                                                                                                                                                                                                                                             | SAS Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45                                                                                          |

|   |                                         | 5.6.6                                                                                                                                                                                                                                                                                                             | Serial Port Connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46                                                                                          |

|   |                                         | 5.6.7                                                                                                                                                                                                                                                                                                             | Keyboard and Mouse Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|   |                                         | 5.6.8                                                                                                                                                                                                                                                                                                             | USB Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |

|   |                                         | 5.6.9                                                                                                                                                                                                                                                                                                             | Telco Alarms Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

| - |                                         |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |

| 6 |                                         |                                                                                                                                                                                                                                                                                                                   | k Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |

|   | 6.1                                     | •                                                                                                                                                                                                                                                                                                                 | Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                             |

|   |                                         | 6.1.1                                                                                                                                                                                                                                                                                                             | CMOS Clear and Password Reset Procedures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                             |

|   |                                         | 6.1.2                                                                                                                                                                                                                                                                                                             | BMC Force Update Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                             |

|   |                                         | 6.1.3                                                                                                                                                                                                                                                                                                             | BIOS Select Jumper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                             |

|   | 6.2                                     |                                                                                                                                                                                                                                                                                                                   | B Port Configuration Jumper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                             |

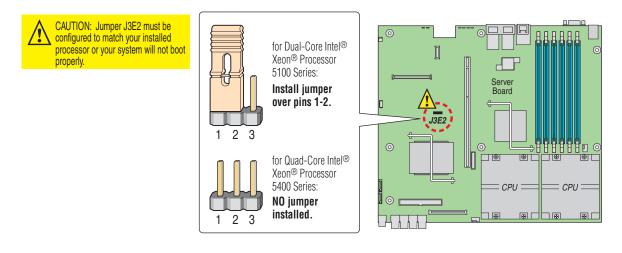

|   | 6.3                                     | Process                                                                                                                                                                                                                                                                                                           | or Select Jumper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51                                                                                          |

| 7 | Light                                   | Guided                                                                                                                                                                                                                                                                                                            | Diagnostics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                                          |

| , | 7.1                                     |                                                                                                                                                                                                                                                                                                                   | ID LED and System Status LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                             |

|   | 7.1                                     | -                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |

|   |                                         | 7.1.1                                                                                                                                                                                                                                                                                                             | System Status LED – Monitored Critical Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                             |

|   |                                         | 7 4 0                                                                                                                                                                                                                                                                                                             | Custom Chatus LED Manitana d Nan Onitical Canalitiana                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

|   |                                         | 7.1.2                                                                                                                                                                                                                                                                                                             | System Status LED – Monitored Non-Critical Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                             |

|   | 7.0                                     | 7.1.3                                                                                                                                                                                                                                                                                                             | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54                                                                                          |

|   | 7.2                                     | 7.1.3<br>DIMM F                                                                                                                                                                                                                                                                                                   | System Status LED – Monitored Degraded Conditions<br>ault LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54                                                                                    |

|   | 7.3                                     | 7.1.3<br>DIMM F<br>Process                                                                                                                                                                                                                                                                                        | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>For Fault LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54<br>54<br>54                                                                              |

|   |                                         | 7.1.3<br>DIMM F<br>Process                                                                                                                                                                                                                                                                                        | System Status LED – Monitored Degraded Conditions<br>ault LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54<br>54                                                                              |

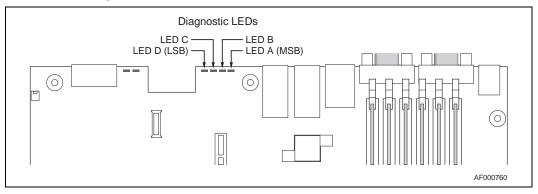

| 8 | 7.3<br>7.4                              | 7.1.3<br>DIMM F<br>Process<br>POST C                                                                                                                                                                                                                                                                              | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>For Fault LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54<br>54<br>54<br>54                                                                        |

| 8 | 7.3<br>7.4                              | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E                                                                                                                                                                                                                                                                  | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED<br>ode Diagnostic LEDs<br>nvironmental Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 54<br>54<br>54<br>54<br>54                                                                  |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S                                                                                                                                                                                                                                          | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                           | 54<br>54<br>54<br>54<br>56<br>56                                                            |

| 8 | 7.3<br>7.4<br>Powe                      | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>Intel <sup>®</sup> S                                                                                                                                                                                                                  | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications<br>Server Board S5000PHB Power Specifications                                                                                                                                                                                                                                                                                                                                                                                             | 54<br>54<br>54<br>54<br>56<br>56                                                            |

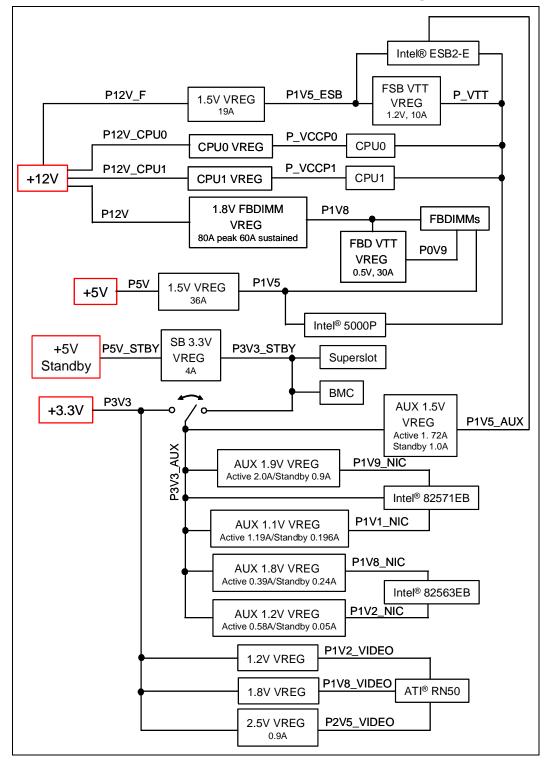

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>r and E<br>Intel <sup>®</sup> S<br>Intel <sup>®</sup> S<br>8.2.1                                                                                                                                                                                                          | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications<br>Server Board S5000PHB Power Specifications<br>Power Distribution                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54<br>54<br>54<br>56<br>56<br>56<br>56                                                |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>r and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2                                                                                                                                                                                                                         | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58                                                |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br><b>er and E</b><br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3                                                                                                                                                                                                        | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>58                                          |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br><b>er and E</b><br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4                                                                                                                                                                                               | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54<br>54<br>56<br>56<br>56<br>58<br>58<br>59                                          |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5                                                                                                                                                                                             | System Status LED – Monitored Degraded Conditions<br>ault LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>58<br>59<br>59                              |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6                                                                                                                                                                                    | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>or Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications<br>Server Board S5000PHB Power Specifications<br>Power Distribution<br>Processor Power Support<br>Output Power / Currents<br>Turn-On No-Load Operation<br>Standby Outputs                                                                                                                                                                                                                                                                 | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>59<br>59<br>59                              |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7                                                                                                                                                                           | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>59<br>59<br>59<br>59                        |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8                                                                                                                                                                  | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>59<br>59<br>59<br>60                        |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.9                                                                                                                                       | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>59<br>59<br>59<br>59<br>60<br>60            |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10                                                                                                                             | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>59<br>59<br>59<br>59<br>60<br>60<br>60      |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11                                                                                                 | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>56<br>56<br>56<br>58<br>59<br>59<br>59<br>60<br>60<br>61            |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.11<br>8.2.12                                                                                               | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>566<br>566<br>558<br>599<br>599<br>600<br>600<br>610<br>61          |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.13                                                                                               | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>566<br>566<br>558<br>599<br>590<br>600<br>601<br>61<br>61           |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br><b>er and E</b><br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.13<br>8.2.14                                                                              | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 54<br>54<br>54<br>56<br>56<br>56<br>555<br>555<br>595<br>595<br>600<br>611<br>61<br>61      |

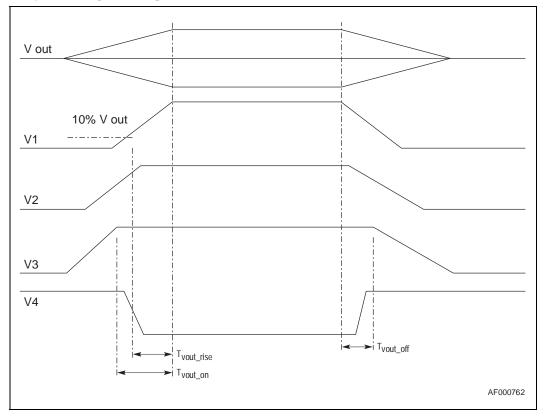

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.11<br>8.2.12<br>8.2.13<br>8.2.14<br>8.2.15                                                       | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                        |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1        | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.11<br>8.2.12<br>8.2.13<br>8.2.14<br>8.2.15                                                       | System Status LED – Monitored Degraded Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                        |

| 8 | 7.3<br>7.4<br><b>Powe</b><br>8.1<br>8.2 | 7.1.3<br>DIMM F<br>Process<br>POST C<br>er and E<br>Intel <sup>®</sup> S<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.13<br>8.2.14<br>8.2.15<br>8.2.16                                               | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>for Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications<br>Server Board S5000PHB Power Specifications<br>Power Distribution<br>Processor Power Support<br>Output Power / Currents.<br>Turn-On No-Load Operation<br>Grounding<br>Standby Outputs<br>Remote Sense.<br>Voltage Regulation<br>Dynamic Loading<br>Closed-Loop Stability.<br>Common Mode Noise.<br>Ripple and Noise<br>Soft Starting<br>Timing Requirements<br>Residual Voltage Immunity in Standby Mode                               | 54<br>54<br>54<br>56<br>566<br>5555<br>599<br>600<br>611<br>611<br>613<br>613               |

|   | 7.3<br>7.4<br>Powe<br>8.1<br>8.2        | 7.1.3<br>DIMM F<br>Process<br>POST C<br><b>er and E</b><br>Intel <sup>®</sup> §<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.11<br>8.2.12<br>8.2.13<br>8.2.14<br>8.2.15<br>8.2.16<br><b>Iatory a</b> | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>for Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications<br>Server Board S5000PHB Power Specifications<br>Power Distribution<br>Processor Power Support<br>Output Power / Currents<br>Turn-On No-Load Operation<br>Grounding<br>Standby Outputs<br>Remote Sense<br>Voltage Regulation<br>Dynamic Loading<br>Closed-Loop Stability.<br>Common Mode Noise<br>Ripple and Noise<br>Soft Starting<br>Timing Requirements<br>Residual Voltage Immunity in Standby Mode<br>and Certification Information | 54<br>54<br>54<br>56<br>566<br>55555555555555555555555555                                   |

|   | 7.3<br>7.4<br><b>Powe</b><br>8.1<br>8.2 | 7.1.3<br>DIMM F<br>Process<br>POST C<br><b>er and E</b><br>Intel <sup>®</sup> §<br>8.2.1<br>8.2.2<br>8.2.3<br>8.2.4<br>8.2.5<br>8.2.6<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.7<br>8.2.8<br>8.2.9<br>8.2.10<br>8.2.11<br>8.2.12<br>8.2.11<br>8.2.12<br>8.2.13<br>8.2.14<br>8.2.15<br>8.2.16<br><b>Iatory a</b> | System Status LED – Monitored Degraded Conditions<br>ault LEDs<br>for Fault LED<br>ode Diagnostic LEDs<br><b>nvironmental Specifications</b><br>Server Board S5000PHB Design Specifications<br>Server Board S5000PHB Power Specifications<br>Power Distribution<br>Processor Power Support<br>Output Power / Currents.<br>Turn-On No-Load Operation<br>Grounding<br>Standby Outputs<br>Remote Sense.<br>Voltage Regulation<br>Dynamic Loading<br>Closed-Loop Stability.<br>Common Mode Noise.<br>Ripple and Noise<br>Soft Starting<br>Timing Requirements<br>Residual Voltage Immunity in Standby Mode                               | 54<br>54<br>54<br>56<br>566<br>5555<br>5555<br>5959<br>600<br>611<br>611<br>613<br>64<br>64 |

|   |      | 9.1.2 Product EMC Compliance – Class A Compliance   |    |

|---|------|-----------------------------------------------------|----|

|   |      | 9.1.3 Certifications / Registrations / Declarations |    |

|   | 9.2  | Product Regulatory Compliance Markings              | 65 |

| Α | Inte | gration and Usage Tips                              | 67 |

| в | Sens | sor Tables                                          | 68 |

| с | POS  | T Codes                                             |    |

| D | Glos | sary                                                | 85 |

| Е | Refe | erence Documents                                    | 88 |

# Figures

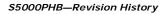

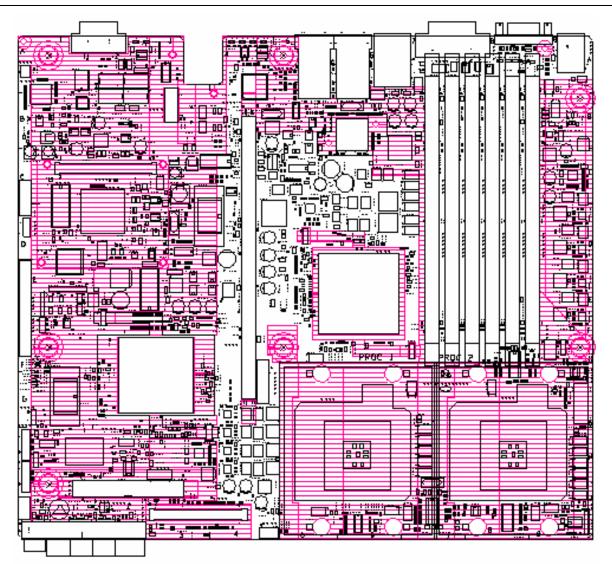

| 1  | Server Board S5000PHB Components and Connector Location Diagram           | 12 |

|----|---------------------------------------------------------------------------|----|

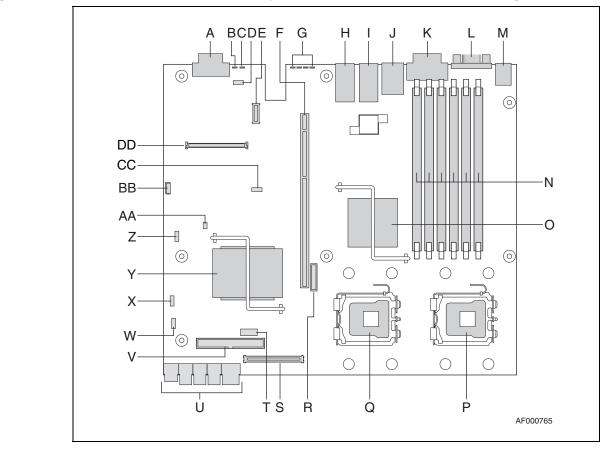

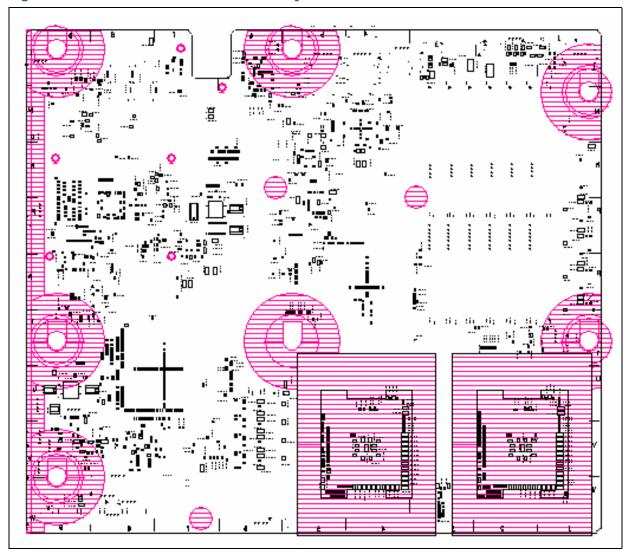

| 2  | Light Guided Diagnostic LED Locations                                     | 13 |

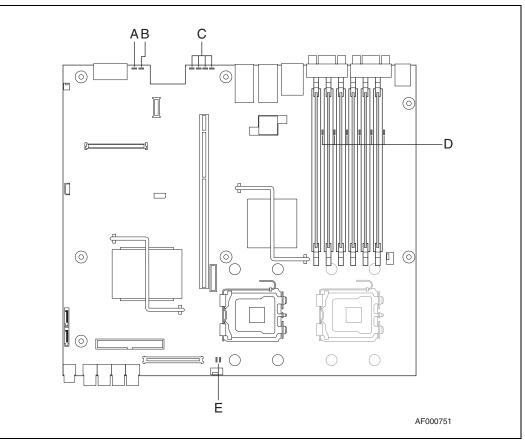

| 3  | Hole and Component Locations                                              | 14 |

| 4  | Restricted Areas on Primary Side                                          | 15 |

| 5  | Restricted Areas on Secondary Side                                        | 16 |

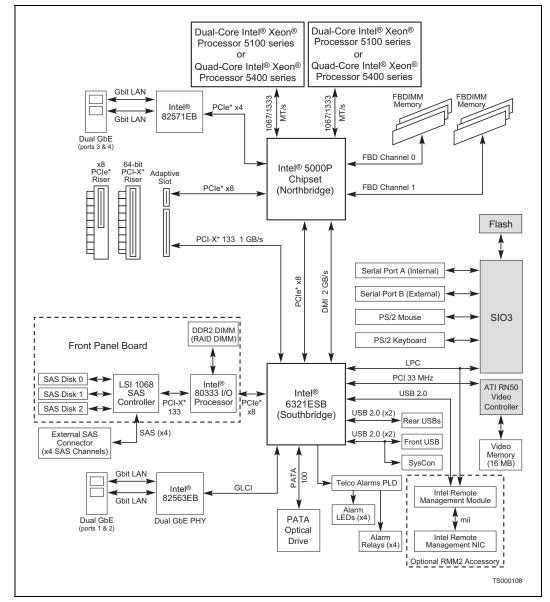

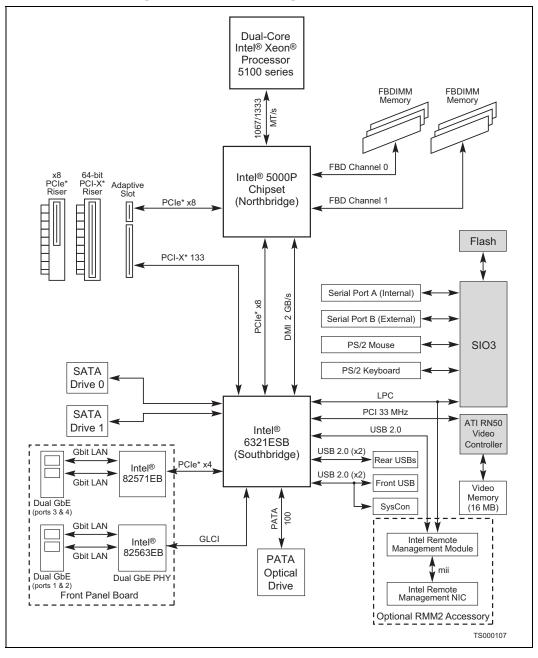

| 6  | Functional Block Diagram, TIGW1U Configuration                            | 18 |

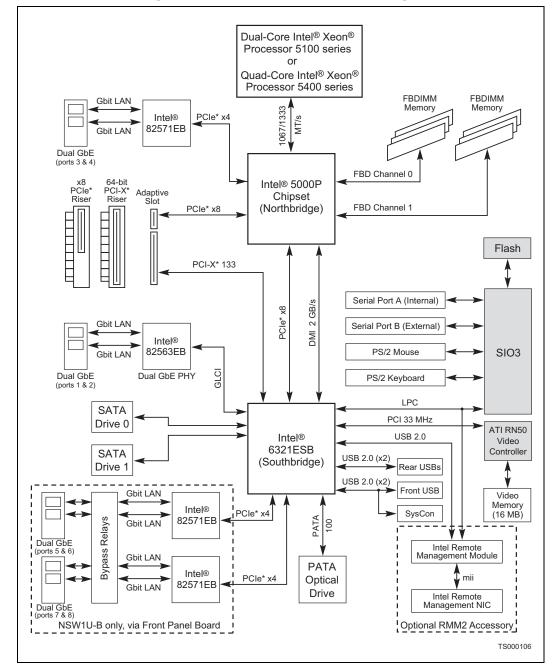

| 7  | Functional Block Diagram, NSW1U-R and NSW1U-B Configurations              | 19 |

| 8  | Functional Block Diagram, NSW1U-F Configuration                           | 20 |

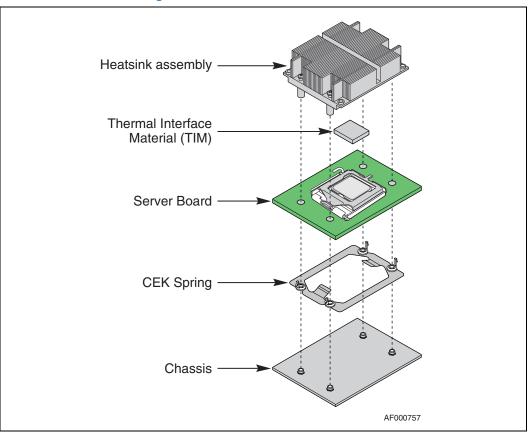

| 9  | CEK Processor Mounting                                                    | 22 |

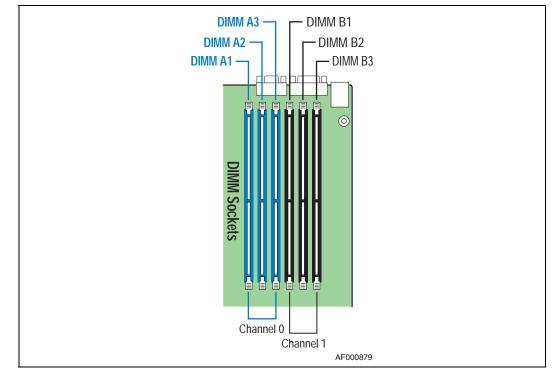

| 10 | Server Board S5000PHB DIMM Slots                                          |    |

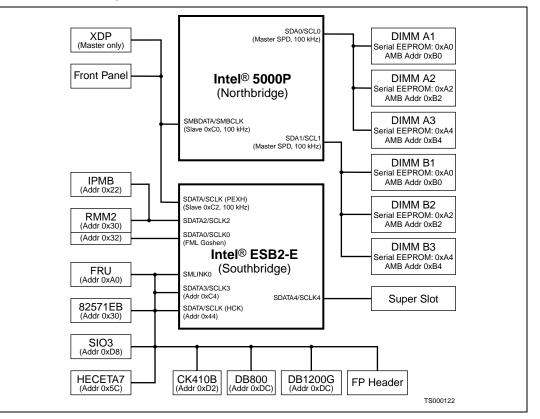

| 11 | SMBUS Block Diagram                                                       | 33 |

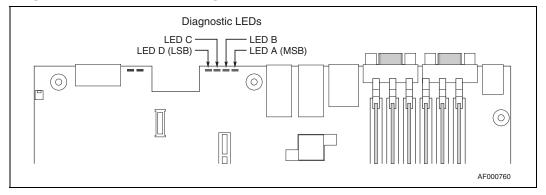

| 12 | POST Code Diagnostic LED Location                                         |    |

| 13 | Intel <sup>®</sup> Server Board S5000PHB Power Distribution Block Diagram | 57 |

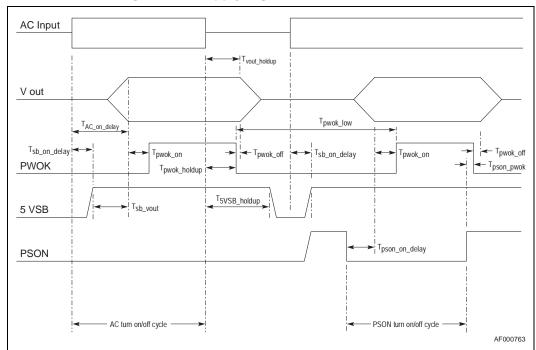

| 14 | Output Voltage Timing                                                     | 62 |

| 15 | Turn On/Off Timing (Power Supply Signals)                                 | 63 |

| 16 | Diagnostic LED Placement Diagram                                          | 78 |

# **Tables**

| Server Board S5000PHB Features       | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C Addresses for Memory Module SMB  | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |